News

dsPIC gets two fast 16bit cores to speed development of high-performance power and motor control

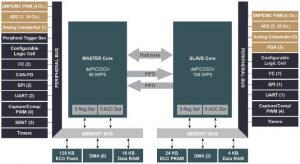

Intended to speed code development by removing dependence between user-interface and real-time code, the cores are largely independent, each with its own set of peripherals, and communicating with each other only via FIFOs and mail-boxes – data and address busses are not shared.

Within dsPIC33CH, as the family will be known, the cores are similar, with one running at 90MHz designated as ‘master’ and a ‘slave’ at 100MHz. The master has more serial interfaces, while the slave has more ADCs, PWM channels and comparators, for example (see diagram).

“The slave core is useful for executing dedicated, time-critical control code while the master core is busy running the user interface, system monitoring and communications functions, customised for the end application,” said the firm. “The dsPIC33CH is designed specifically to facilitate independent code development for each core by separate design teams and allows seamless integration when they are brought together in one chip.

Potential applications include digital power and motor control, for example in wireless power, servers, drones and automotive sensors.

In a digital power supply, according to Microchip, the slave core manages the maths-intensive algorithms, while the master core independently manages the PMBus protocol stack and provides system monitoring. In an automotive fan or pump, the slave core would manage time-critical speed and torque control while the master manages CAN-FD (CAN-flexible data-rate) communication, system monitoring and diagnostics.

Live (‘zero down-time’) firmware upgrades are made possible on both cores because each of them has two flash programme stores – four in total.

If live-upgrades are not needed, double the amount of programme memory is available to the core.

Compared with the previous dsPIC family aimed at the same market – dsPIC33EP/GS – performance is almost doubled (latency down from 543ns to 280ns) – partially through clock speed rising from 70MHz to 100MHz and partially through: faster context switching (context-sensitive accumulators and status registers) and new instructions (faster divide, 32bit load/store).

There are eight package variants, from the 28pin dsPIC33CH64MP202 up to 80 pins, and from 5 x 5mm upwards.

Flash options span 64 to 128kbyte.

Support comes from:

- MPLAB X IDE

- Code Configurator

- dsPIC33CH Curiosity Board (DM330028)

- dsPIC33CH plug-in module for motor-control (MA330039) for MCLV-2 and MCHV-2/3

- dsPIC33CH plug-in module for general-purpose platforms (MA330040) for Explorer 16/32 (DM240001-2)